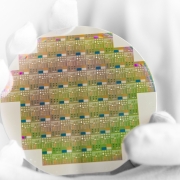

晶圆代工龙头台积电第三季法人说明会将于17日登场,由总裁魏哲家及新任财务长黄仁昭共同主持。台积电今年资本支出维持在110亿美元高标,市场预期将聚焦5奈米大投资计划,包括Fab 18厂第一期于明年3月之后进入量产,第二期及第三期产能建置会在明、后两年完成并投入量产,2022年全产能投片下5纳米晶圆年产能将逾100万片规模。

设备业者推估台积电2020年资本支出将上看120~130亿美元,最主要投资项目是5纳米极紫外光(EUV)产能建置,且2021年资本支出将因Fab 18厂3纳米项目启动而持续提升。

法人看好包括厂务工程厂汉唐、再生晶圆厂昇阳半及中砂、EUV光罩盒厂家登、晶圆测试卡厂精测、硅晶圆厂环球晶、检测服务厂宜特及闳康等台积电大联盟伙伴直接受惠。

台积电5纳米可说是集技术之大成。其7纳米加强版(N7+)已採用EUV微影技术量产,因已走过新技术学习曲线,5纳米导入EUV速度加快且良率提升符合预期。与7奈米制程相较,5纳米晶片密度增加80%,在同一运算效能下可降低15%功耗,在同一功耗下可提升30%运算效能。而且,5纳米也首度采用极低临界电压(ELVT)电晶体的超低功耗设计,在ELVT运算下仍可提升25%运算效能。

再者,台积电会在5纳米量产后一年推出5纳米加强版(N5+),与5纳米制程相较,在同一功耗下可再提升7%运算效能,或在同一运算效能下可再降低15%功耗。N5+制程将在2020年第一季开始试产,2021年进入量产。

台积电亦会在5纳米制程世代,搭配推出3D芯片封装制程,以因应客户在高效能运算及5G等应用需求,其中包括相同晶片尺寸及製程的晶圆堆叠晶圆封装、芯片堆叠在晶圆上的系统整合单芯片封装等两大主轴。业界看好台积电3D芯片堆叠封装方案,能够整合多个非常邻近的异构小芯片并提供更佳的系统效能。

据法人推测,台积电将5纳米是7纳米之后重大节点,在芯片密度、运算效能、降低功耗等各方面提升均有显著效益,包括苹果、华为海思、超微、赛灵思(Xilinx)、英伟达(NVIDIA)、博通等大客户都会委由台积电量产5纳米芯片或处理器,至于高通5纳米订单预期也将重回台积电投片。

来源:内容来自「工商时报」,谢谢。

内容声明:除原创作品外,本平台所使用的文章、图片、视频及音乐属于原权利人所有,因客观原因,或会存在不当使用的情况,如部分文章或文章部分引用内容未能及时与原作者取得联系,或作者名称及原始出处标注错误等情况,非恶意侵犯原权利人相关权益,敬请相关权利人谅解并与我们联系及时处理,共同维护良好的网络创作环境。