摩尔定律失效,芯片性能提升遇瓶颈

在探讨Chiplet(小芯片)之前,摩尔定律是绕不开的话题。戈登·摩尔先生在1965 年提出了摩尔定律:每年单位面积内的晶体管数量会增加一倍,性能也会提升一倍。这意味着,在相同价格的基础上,能获得的晶体管数量翻倍。不过,摩尔先生在十年后的1975年,把定律的周期修正为24个月。至此,摩尔定律已经影响半导体行业有半个世纪。

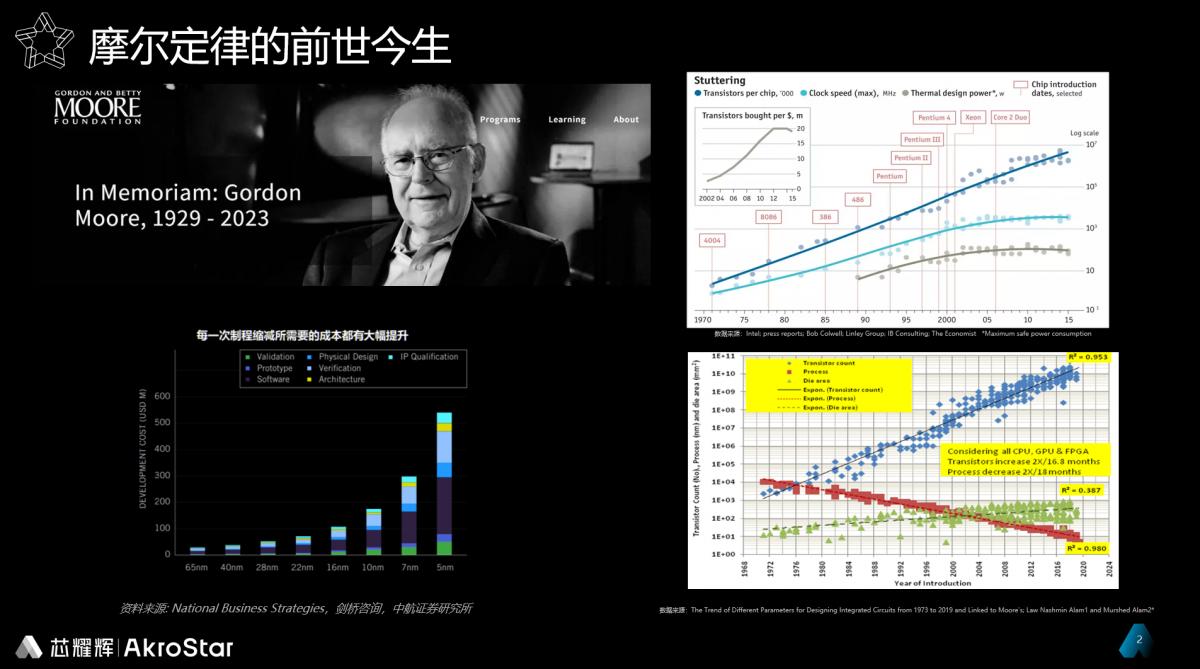

随着集成电路技术的不断演进,半导体行业发现摩尔定律在逐渐失效。上图右上部分是英特尔x86 CPU 1970-2025年的演化历史,可看出每颗芯片的晶体管数量持续增加(右上深蓝色线条),但时钟速度(右上天蓝色线条)和热设计功耗(右上灰色线条)自2005年之后就变化不大。于此同时,受先进工艺高成本支出的影响,晶体管成本降幅在2012年后趋缓,甚至越往后还有成本增加的趋势。

从上图右下的统计数据可看出,芯片制程在持续微缩和演进,晶体管数也在相应的增长。在2019年以前,单芯片晶体管数量和工艺几何尺寸演进,一直与摩尔定律高度相关。因为单位面积内的晶体管数量,每一周期就会增加一倍,所以在理想情况下,Die的尺寸可保持不变。但是据右下绿色标识的区域显示,可以看到单芯片Die尺寸在日趋增大,这也从另一个角度说明,单芯片晶体管数量的增加,也有Die增大的原因所致。由于Die尺寸的增长,受光罩尺寸、工艺良率等因素制约,这代表通过加大Die Size来提升单芯片算力已经越来越困难。

总而言之,随着集成电路技术的发展和演进,每24个月已经很难让单位面积内的晶体管数量翻倍。这意味着,现在芯片性能的提升遭遇了瓶颈,性能无法单纯由工艺技术驱动,也需要由架构创新来驱动。因此,业界必须找到新的解决方案。

Chiplet帮助芯片生产降本增效

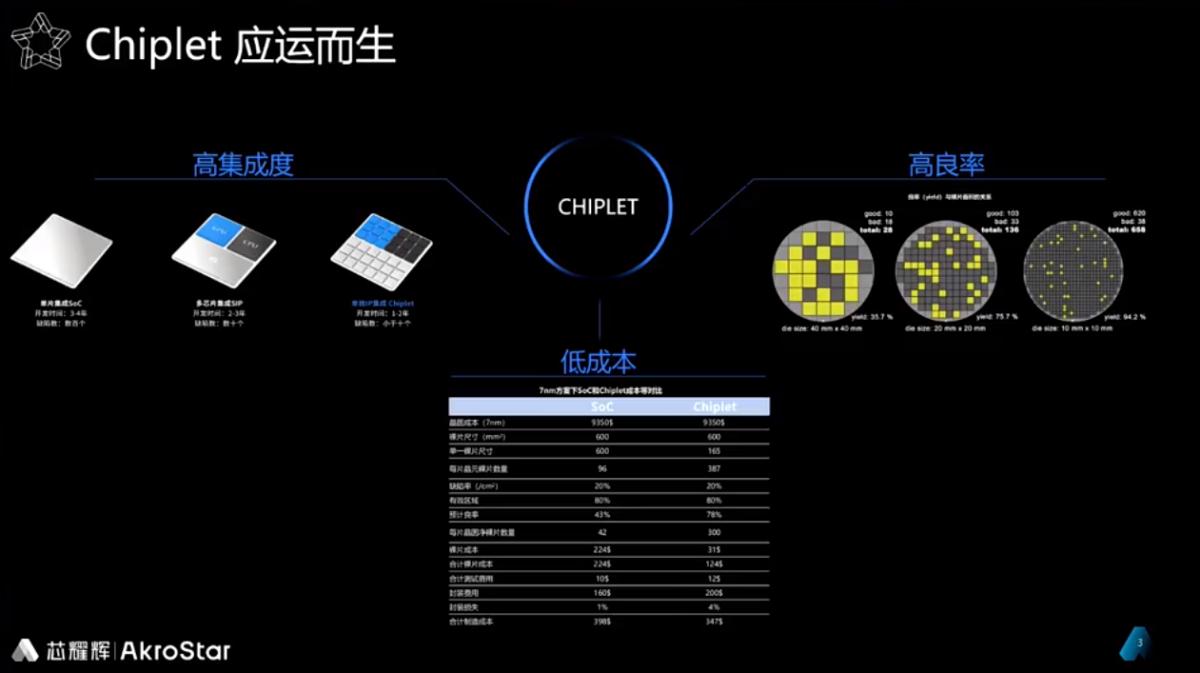

在摩尔定律逐渐失效的情况下,Chiplet技术在半导体行业应运而生。整体来看,Chiplet具备高集成度、高良率、低成本三大特点,它被视为延续摩尔定律的关键技术。

曾克强介绍说,Chiplet通过多个芯片的片间集成,可以突破传统单芯片的上限,进一步提高芯片的集成度。比如,左上图的单片集成的SoC是通过统一工艺制程,导致芯片上各个部分都要同步进行迭代,其开发时间长达三至四年,缺陷数量可达数百个。左上图的单独IP集成Chiplet通过将不同的功能切开,再对部分单元的工艺做选择性迭代,迭代裸片后可制造出下一代产品,这样就能加速产品的上市周期。Chiplet芯片集成应用较为广泛和成熟的裸片,就有效降低了Chiplet芯片研制风险,也减少了重新流片和封装的次数,进而能为芯片企业节省研发投入。

Chiplet可以提升复杂SoC芯片的良率,该方案将复杂SoC芯片分成更小的芯片。单芯片的面积越大其良率越低,它对应的芯片制造成本也就越高,芯片设计成本也会随着制程的演进而成本增长,切割小芯片可有效降低芯片设计成本。此外,在SoC设计中,模拟电路、大功率IO对制程并不敏感,不需要太高端的芯片制程,可将SoC中的功能模块,划分成单独的Chiplet,针对功能来选择合适的制程,从而让芯片实现最小化,提高芯片的良率、降低芯片成本。

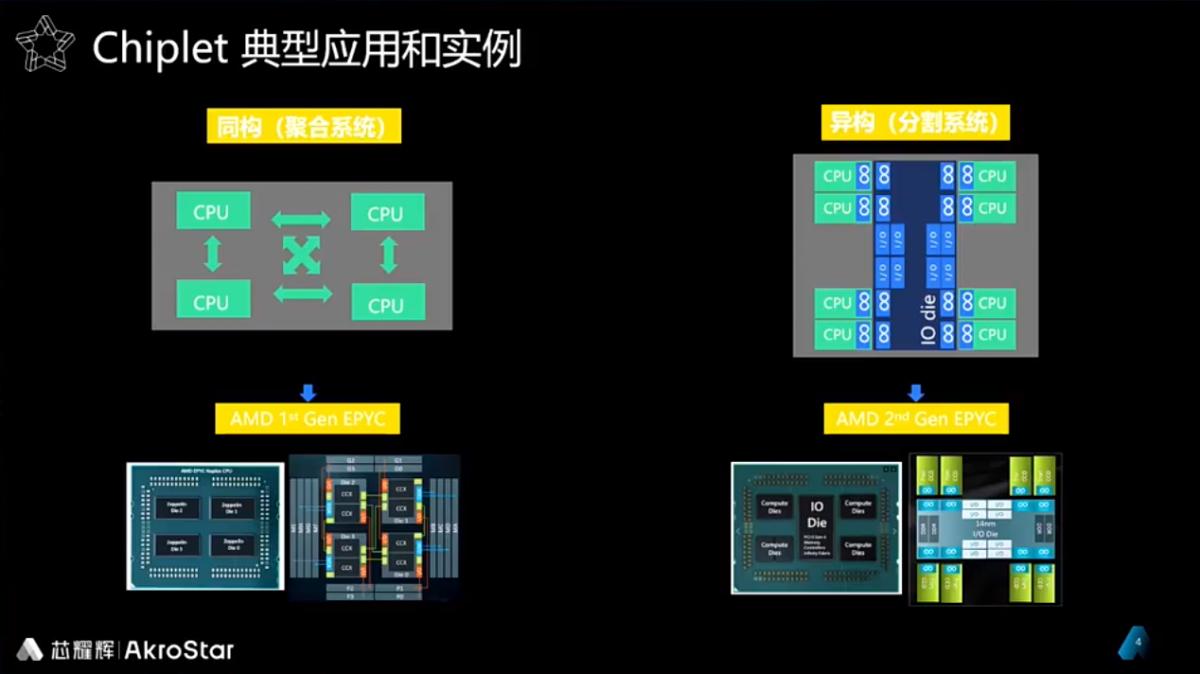

Chiplet有两个常见的应用案例:同构(聚合系统)和异构(分割系统)。同构是通过高速接口和先进的封装技术,适用于CPU、TPU、AI SoC等,这种方式是将多个Die紧密相连,以相同的Die设计实现计算能力的扩展,其接口要求低延迟和低误码率;异构是将芯片按功能拆分,先进制程的Die提供高算力和性能,成熟制程的Die负责常规或者特色的功能,这些不同制程的Die被封装在一起。

在使用案例方面,AMD服务器CPU Epyc系列的第一代和第二代,分别采用了同构和异构的方法。第一代Epyc采用7nm制程,利用同构方法聚合4个相同的Die,该系统可扩展,只需多个Die的互联,即可提高计算能力;第二代 Epyc将芯片功能拆分为CCD运算Die(Compute Core Die)和IO Die,通过异构方法它们集成到一起,实现了先进工艺与成熟工艺的巧妙融合。

通过高速接口和先进封装技术,把多颗Die融合在一颗大芯片内,以此来实现算力的扩展,这适用于CPU、FPGA、通信芯片等产品。同时,Chiplet也对接口提出了标准化、兼容性、可移植性的要求,要具备低延时和低误码率的优势,厂商选择接口时还需考虑生态系统问题。

曾克强总结说:“Chiplet可提升大芯片设计良率,降低芯片研发的风险,缩短芯片的上市时间,还可增加芯片产品组合,延长产品生命周期。因此,它被视为有效延续摩尔定律的新方式。”

Chiplet的发展趋势及生态布局

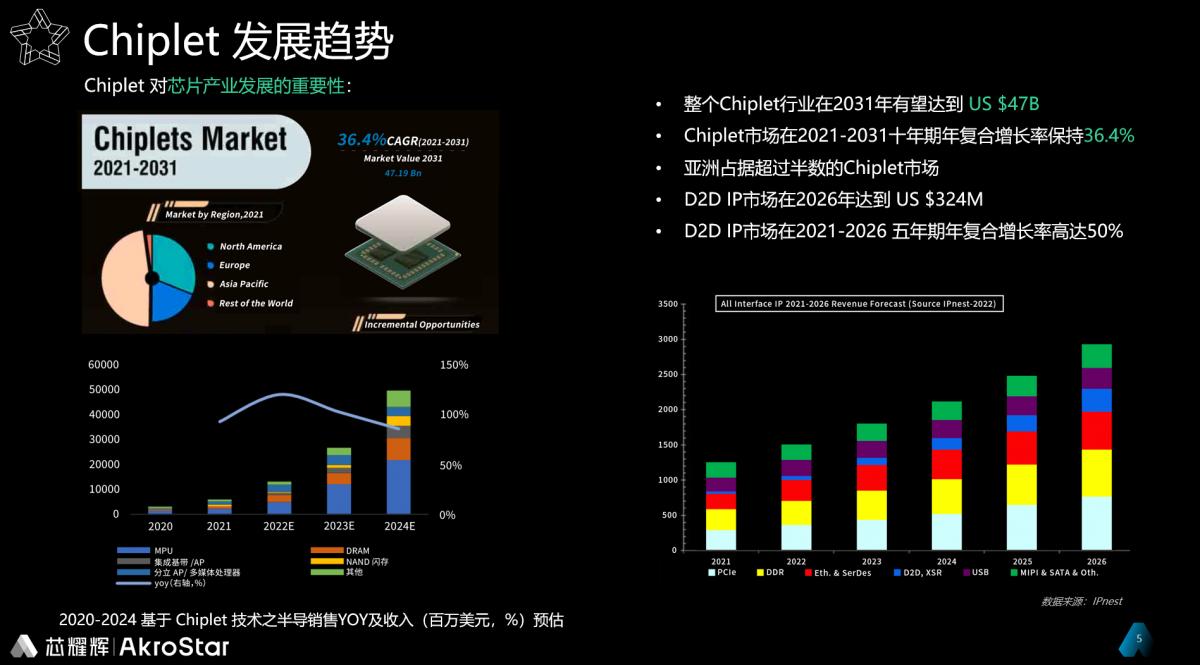

Chiplet应用在芯片中的时间还不长,但自2020年开始其发展就非常快,年复合增长率达到36.4%。预测到2031年,全球Chiplet行业市值有望达到470亿美元(上图左边)。

因为Chiplet把芯片切分成不同的小芯片并互联,所以相关接口IP市场也有新的需求。上图右边是各类传统接口IP市场的发展趋势,蓝色方块体现了小芯片互联接口IP的趋势。虽然小芯片互联接口IP的发展时间较短,但是其增长速度最为迅猛,预计从2021年到2026年,年复合增长率会高达50%。至2026年,全球产值将达3.2亿美元。

Chiplet技术需要切分、堆叠整合,该技术将推动芯片产业链的变革。曾克强预测,Chiplet的发展将分为几个阶段:2023年之前的两三年是Chiplet生态早期阶段,芯片公司对芯片进行分拆,并寻找先进封装组合,各家都按自己的定义协议来做产品,该阶段并未形成统一的标准。

进入到2023年,随着工艺制程进入3纳米接近物理极限,摩尔定律失效越来越明显,而摩尔先生的去世,似乎也在印证旧时代正在落幕。与此同时,属于Chiplet的新时代正在开启。设计厂商对自己设计的Chiplet进行自重用和自迭代,同时工艺逐渐成型,互联标准日趋统一。

预计到2027年,Chiplet生态将进入成熟期,真正进入IP硬化时代。届时,会诞生一批新公司:Chiplet小芯片设计公司、集成小芯片的大芯片设计公司、有源基板供应商、支持集成Chiplet的EDA公司。

主要有四个重要角色参与Chiplet生态链:EDA供应商,IP厂商,封装厂,Fab厂。尤其对于IP供应商而言,基于IP复用的模式,设计能力较强的IP供应商有潜力演变为Chiplet供应商。而IP供应商也需要具备高端芯片的设计能力,以及多品类的IP布局和平台化的运作能力,以上都对IP供应商提出了更高的要求。又由于Chiplet加入了更多的异构芯片和各类总线,相应的EDA覆盖工作就变得更加复杂,需要更多的创新功能。国内EDA企业需要提升相关技术,应对堆叠设计带来的诸多挑战,例如对热应力、布线、散热、电池干扰等的精确仿真,在封装方面需要2.5D和3D先进封装技术支持,同时Fab方面也需要相关技术的支持。

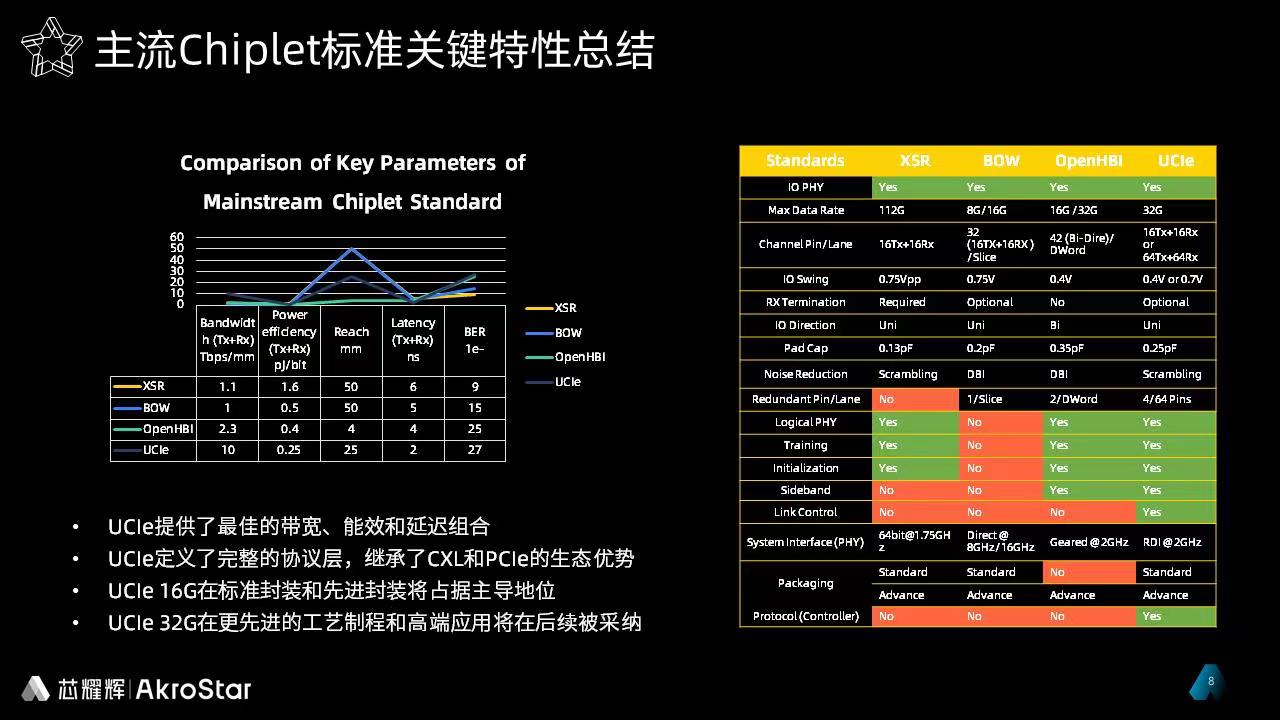

经过了几年的发展,国际上出现了一些Chiplet标准,主流标准包括XSR、BOW、OpenHBI、UCIe(详见上图右表)。右表中的绿色代表技术优势,红色代表劣势。可以看出UCIe标准在多个角度都占据优势,它定义了逻辑 PHY、训练机制、初始化序列、边带和链路控制。此外,它还重用了成熟的PCIe和CXL生态系统,这将加快这一新标准的采纳,并得到代工厂、封装厂、无晶圆厂和系统公司的支持。

从左侧的图表中可以看出,UCIe提供了最高带宽、最佳能效比和最低延迟的最佳组合。具体来看,UCIe定义了完整的协议层,继承了CXL和PCIe生态系统的优势。UCIe 16G将主导标准封装和先进封装行业,UCIe 32G将在更先进封装工艺和高端应用方面将被采纳。

如何解决Chiplet面临的挑战

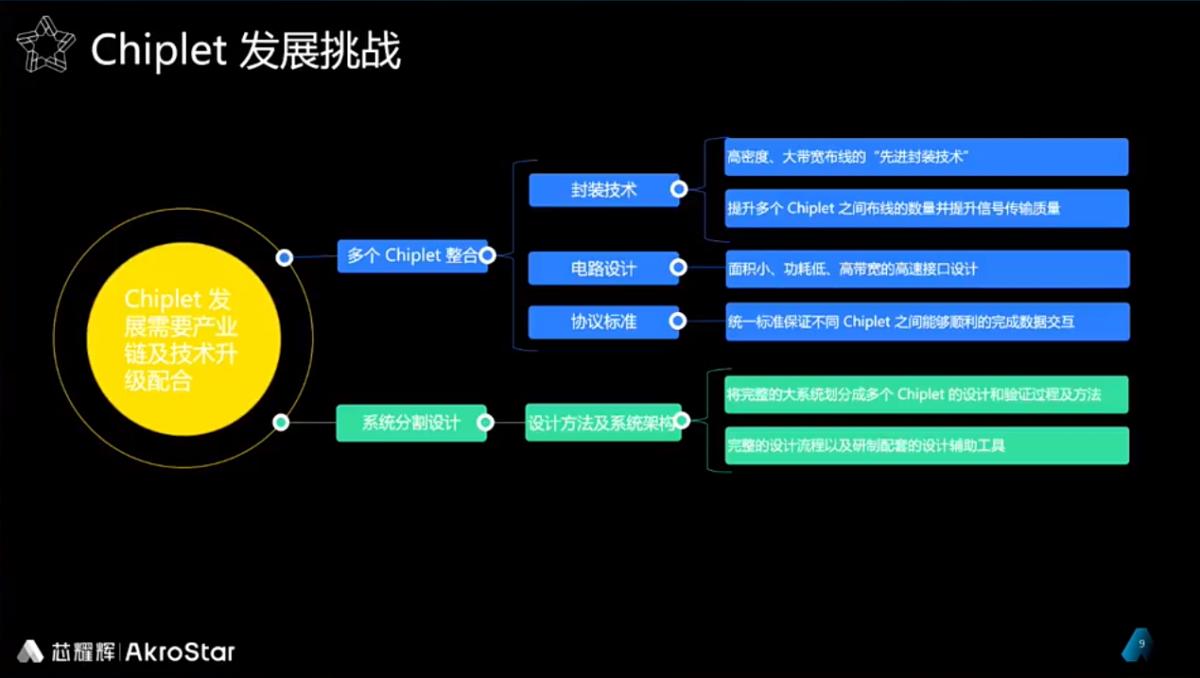

Chiplet的发展刚起步不久,还面临着非常多的挑战,它需要产业链及技术升级配合。这些挑战主要分为两大类:上图蓝色部分展示的是多个Chiplet堆叠整合的挑战,绿色部分是怎么系统分割设计方面的挑战。

堆叠整合往下还细分为封装技术、电路设计、协议标准三方面的挑战。

首先,Chiplet技术把单个大硅片“切”成多个小芯片,再把这些小芯片封装在一起,单颗硅片上的布线密度和信号传输质量远高于不同小芯片,这就要求必须要发展出高密度、大带宽布线的先进封装技术,尽可能提升在多个Chiplet之间布线的数量并提升信号传输质量。Intel和台积电都已经有了相关的技术储备,通过中介层(Interposer)将多个Chiplet互连起来,目前这些技术仍在不断演进中,并在不断推出更新的技术。

其次,用于Chiplet之间的高速通信接口电路设计。Chiplet之间的通信虽然可以依靠传统的高速Serdes电路来解决,甚至能完整复用PCIe这类成熟协议。但这些协议主要用于解决芯片间甚至板卡间的通信,在Chiplet之间通信用会造成面积和功耗的浪费。

再次,通信协议是决定Chiplet能否“复用”的前提条件。Intel公司推出了AIB协议、TSMC和Arm合作推出LIPINCON协议,但在目前Chiplet仍是头部半导体公司才会采用的技术,这些厂商缺乏与别的Chiplet互联互通的动力。目前,UCIe联盟最重视协议,如果实现了通信协议的统一,IP公司就有可能实现从“卖IP”到“卖Chiplet”的转型。

先进封装解决了如何“拼”的问题,更重要的是要解决如何“切”的问题。英伟达在决策下一代GPU要采用Chiplet技术时,思考和验证如何把完整的大芯片设计划分成多个Chiplet,这其实是设计方法学的初步体现。要让基于Chiplet的设计方法从“可用”变为“好用”,需要定义完整的设计流程,以及研制配套的设计辅助工具。

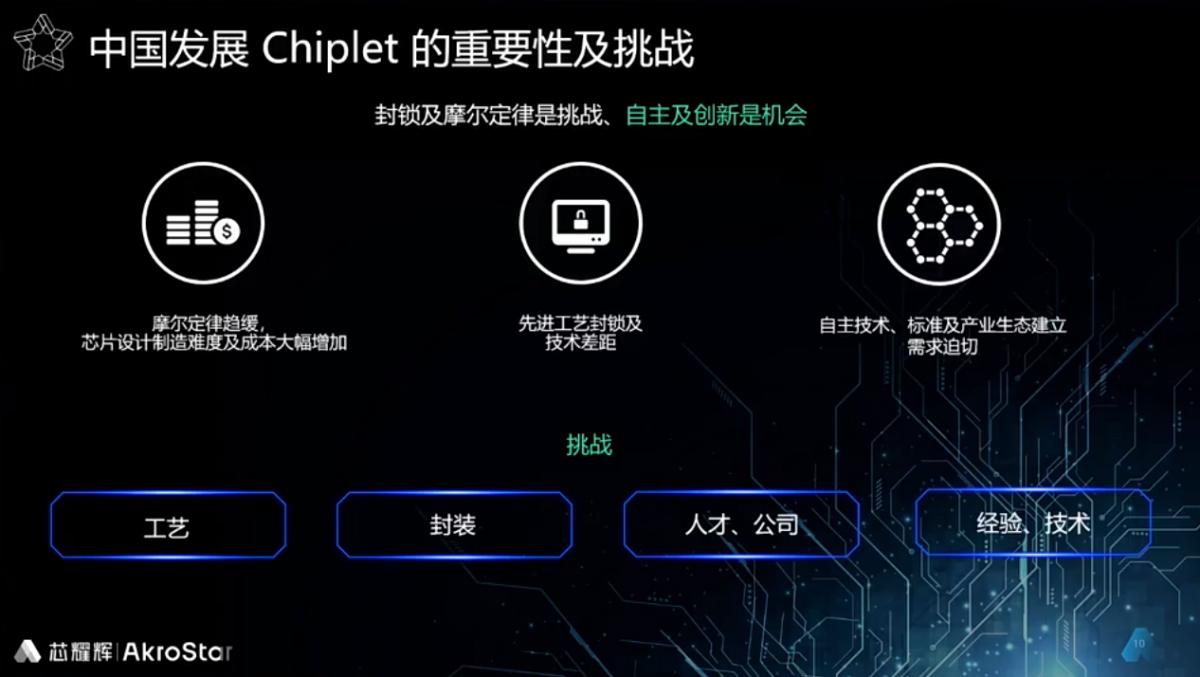

在中国发展Chiplet面临哪些挑战?从技术上面看来,中国现在产业链发展最大的挑战是技术封锁,由封锁所带来的自主需求也是一大机遇。在单位硅片面积上增加晶体管数量有困难,转而追求在单个封装内部持续提升晶体管数,这也是目前发展Chiplet技术对国内芯片产业的最大意义。

但是现在我们仍缺乏必要技术、经验、标准协议、人才、知识产权和专利积累,而且中国芯片公司的规模都不大,无法单靠某一家或某几家公司来打造Chiplet生态。这需要不同的公司分工合作,共同打造Chiplet产业链。

中国要发展自己的Chiplet生态链就需要有自己的标准。国内的CCITA联合集成电路企业和专家,共同主导定义了小芯片接口总线技术要求,这是中国首个原生Chiplet标准,在去年12月15日通过了工信部电子工业标准化技术协会的审定并发布。

该标准与UCIe主要有两大区别:UCIe只定义了并口,CCITA的Chiplet标准既定义了并口,也定义了串口,两者的协议层自定义数据包格式也不同,但CCITA的标准与UCIe兼容,可直接使用已有生态环境。在封装层面,UCIe支持英特尔先进封装、AMD封装,CCITA定义的Chiplet标准主要采用国内可实现的封装技术。

芯耀辉的接口IP方案

据曾克强介绍说,芯耀辉参与协议组织推动Chiplet发展,作为重点贡献企业参与了标准协议制定与推广,以此确保其产品和研发能力始终走在产业发展最前沿,依靠对标准协议深度理解,能给产业带来更多优秀的IP产品。

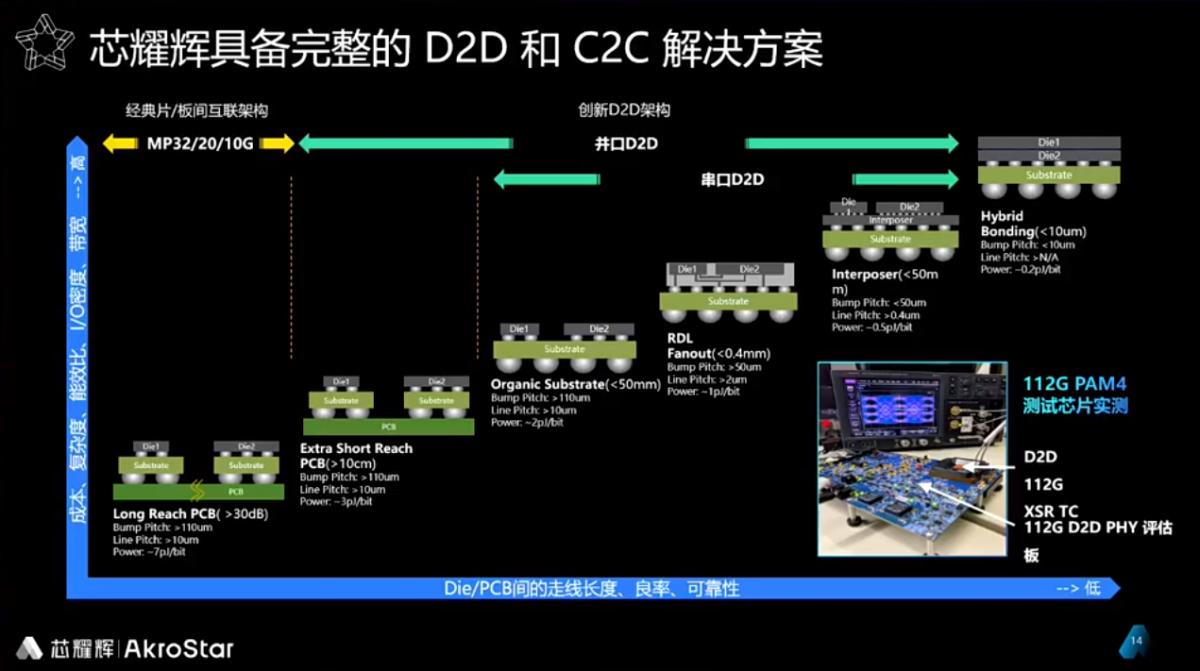

比如,芯耀辉D2D IP把互连扩展到短距离PCB,以满足中国本地市场需求。D2D IP解决方案涵盖绿色箭头所示的全部封装类型,与目前国内生产加工能力高度适配,目前112G PAM4测试芯片已经成功实测。

曾克强表示,Chiplet不只是简单的IP技术,也包括整个系统的设计和生产测试,比如子系统的设计、封装设计、PCB设计、ATE测试等等。芯耀辉从一开始做IP设计时,就把SoC集成、系统应用需求及下游封装测试等对Chiplet的要求转化为对IP设计规格的要求,一开始就考虑到后端要实现Chiplet所需要的特性,从IP源头来解决这些挑战。比如说从控制器、PHY、子系统方面来实现高性能、低功耗、低延迟,一般供应商会追求最佳的PPA,但客户产品应用不一样对PPA的需求也不一样,所以我们提供可灵活配置的PHY,更适配客户的特定应用,帮助不同的客户都能得到适合自己的最佳PPA。并且对关键的与频率相关的部分,我们提供的都是硬核,保证客户的时序收敛。另外,我们在PHY中还嵌入了许多在Silicon之后的测试功能,特别是大家都关注的KGD(Know Good Die)测试,因为在一个封装里面多个Die互联以后,没法像常规芯片一样放探针来确定里面的Die是否正常工作或者Die与Die之间的互联是否出现短路,所以我们的PHY提供了丰富的D2D KGD测试功能。还有控制器和子系统也是如此,我们都是在IP设计的源头就来解决这些挑战,而不是将挑战推向系统设计和生产测试以适应IP。这样就提供了完整的解决方案,加快客户芯片上市时间和一次流片成功率。

目前,D2D IP已经实现客户项目的成功量产,主要有数据中心、5G、网络交换机应用,客户项目导入的实例类似AMD第一代服务器,采用的是同构聚合方式来实现多个Die的互联。