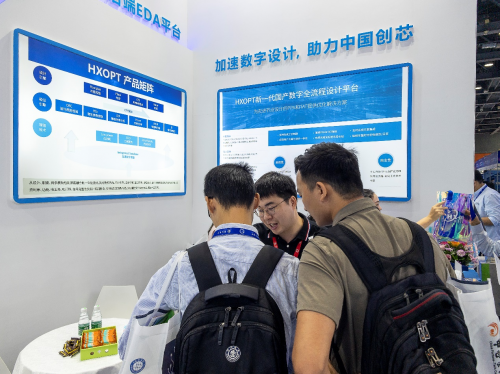

11月11日,中国集成电路设计业2023年会暨广州集成电路产业创新发展高峰论坛(ICCAD 2023)在广州圆满落幕本次会议规模创历史之最,参会人数也再创新高,吸引了众多国内外知名EDA企业。华芯巨数受邀受邀亮相本次展会,展示数字后端设计EDA产品和技术,与业内伙伴探讨EDA行业的创新与发展。

华芯巨数展示了HXOPT新一代国产数字后端设计EDA平台。该平台提供从RTL到GDS的数字后端设计全流程解决方案,包括布图规划、布局、时钟树综合、布线的完整流程以及时序、物理、功耗的分析功能,为设计的性能、功耗、面积(PPA)等关键指标提供优化解决方案,提供更优TAT,支持多个主流及先进工艺制程。平台以业界标准文件格式为输入,提供用户友好的脚本配置和设计流程。特有的Litho Friendly Design技术在后端设计流程中引入对光刻效果的考虑,为产品良率提供有力保障。

华芯巨数的技术研发一部总监刘通博士在会上带来“新一代数字后端设计EDA平台”的主题演讲。针对如何更好地支持国内芯片产业的问题,华芯巨数的建议是在技术上追赶三大家的同时,需要加强设计工具前后端的联系、设计工具与制造工具的联系,通过流程的协同优化,实现设计结果的提升。因此,在主体开发后端设计工具实现芯片后端全流程设计的同时,华芯巨数致力于改进后端设计工具与前端设计以及制造端工具的协同优化流程,为芯片后端设计与验证提供良率驱动的国产化全流程解决方案。

在后端设计流程的功能支持之外,华芯巨数也开展了与前端设计工具以及与制造端工具的协同优化工作,试图打造从RTL到wafer的一体化的芯片设计平台。通过与前端设计工具结合,在HXOPT中实现re-synthesis的功能。借助前端设计对网表的重构与优化功能,优化后端设计过程中的时序最差路径,进而提升整个设计结果的质量。通过与制造端计算光刻(OPC)工具结合,在HXOPT中实现光刻优化布线的功能。基于OPC工具对于工艺行为的精准预测,在后端设计阶段提前发现光刻坏点并进行设计修复,得到制造端更加优良的结果,提高流片良率。

刘通指出自“十四五”明确提出EDA是重点需要突破的基本软件,实现芯片设计工具安全、自主、可控已上升至国家战略。在面临这样的产业困境的同时,国产化EDA工具的实现也可以改变国内市场有国外三大家厂商垄断的局面,国内市场的国产化替代空间极大。在这样的挑战与机遇下,国内陆陆续续成立了上百家EDA公司。如何越过三大家的技术壁垒并满足国内芯片产业对于EDA工具的需求,是所有EDA公司需要考虑的事情。

华芯巨数(杭州)微电子有限公司位于杭州滨江区,在武汉、北京及美国硅谷设立研发中心,认定为科技型中小企业和浙江省创新型中小企业。公司致力于提供良率驱动的数字后端设计与验证的全流程解决方案。通过自主研发、技术引进和商业模式的创新,华芯巨数提供具有国际领先水平的EDA解决方案,为合作伙伴提供安全可靠的产品和服务,助力中国集成电路产业的发展。