跟前些年一样,国产 GKJ 每一年总是有许多各类突破消息层出不穷,2023年7月份新*社发布28nm光K机2023年底交付,一时炸了锅 , 最终确认只是一个炒股的小作文 , 经过证卷日报以此为题完善了报导 , 随后新*社跟进转发 , 并在沸沸扬扬几天后新*社自行删帖 , 作者当时发文澄清并阐述了目前国产 GKJ 的实际进展,官* 媒的不靠普及不严谨可见一般 。

紧接着2023年9月清华前两年的一篇SSMB论文引起市场广泛讨论光刻厂的可能性,本来想趁热点写篇光刻厂的文章,但无奈一直挺忙,空闲时间又懒,所以一直没针对所谓SSMB写点什么,2023年底Canon发布可以达5奈米制程节点的奈米压印机FPA-1200NZ2C , 让作者思考了一下倒底同步辐射,纳米压印又或者坚持传统光刻技术路线,哪一个才是解决中国半导体的老大难问题”GKJ”的最好路径 。

国产GKJ , 某大厂已经投入好几年 , 上海嘉定厂也进入好几台Nikon 635的浸没式 , 不过纯国产浸没式目前具备能进Fab做alpha的样机还出不来 , 未来有机会在知识星球再写写目前国产GKJ的真实现况与进度。有兴趣的可以自己搜搜

半导体行业进入EUV时代将波长已经一口气推进到接近X-ray波长的上限,再要缩短波长恐怕要用新的物理机制产生新的光源,上述三种路线各有优点也又各有缺点 , 而中国在被西方限制,无法取得先进光刻机的情况下,应该如何发展?

同步辐射可以做为光刻机光源吗?

2023年9月被网友夸大为光刻厂的就是位于北京怀柔的中科院高能所正在兴建中的第四代同步辐射装置跟才规划完成的清华雄安SSMB-EUV项目。网上绘声绘影的把光刻厂描绘为,一力降十会,大力出奇迹,跳过EUV的三大难点其中的两点 , 光源跟物镜,只要保证双工作台的精度就行,在Fab外部建设超大型的同步辐射光源厂,直接上KW级的8nm波长,实现光源外置和Fab集群的共享,光刻机则从外部接入合适的功率和波长的光,完成高精度光刻。

然而中科院高能所早于1984年开始在北京玉泉路兴建第一代同步辐射装置,随后也一直有迭代跟升级。这已经是近40年前的旧事。

同步辐射是高能物理实验仪器的另类应用。原先的应用是利用电场加速电子,利用磁铁弯曲电子行径,并依圆形轨道运行。加速后的带电粒子对撞生基本粒子,主要是魅夸克(charm quark)。

由于带电粒子被加速时会放出电磁波也就是光,同步辐射装置也可以利用这些光探测材料及生物结构,这是目前的几个应用范畴。但是谈及应用于光刻机的光源那又是另外一回事了。

考虑用同步辐射来当光刻机光源绝对不是新鲜事,X-ray光阻早在80年代就是研究的题目。90年代业界在考虑未来光刻机的光源时,EUV和同步辐射都是曾被考虑的方向。

当初美国国防部高等研究计划署(DARPA)选择EUV,但是也有其他公司选择同步辐射,譬如IBM。在重新检视同步辐射是否适合当光刻机光源时,让我们简单回顾一下EUV的几个特性。

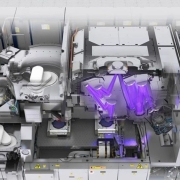

EUV光刻机

EUV一般是指波长于121~10nm的光,波长再短就是X-ray了。在EUV波长区域,并没有天然的材料与机制可以产生激光,现行的13.5nm EUV是以二氧化碳激光照射掉落的锡液滴所激发的次级光源。

由于EUV光的产生过程复杂,光的频率集中的程度远不如使用激光源的DUV,亮度也远远不如DUV。亮度不足,曝光时间就需要较长,这就影响了光刻机产出效率(WPH)。

由于EUV光的能量较DUV高,容易透镜材料发生反应而被吸收,光的传递依赖于好几个有多层镀膜的反射镜组形成光路并聚焦。对于半导体产业而言,这是一个有别于之前基于激光光源的全新的光学系统,这也说明为什么EUV理论早就证明可行但却要发展20余年才得以商业化的原因。

即使用全反射镜来建立光路,垂直镜面入射的光线仍然会被部分吸收。因此,光线最好以与镜面垂直线倾斜6、7度的角度入射。由于这个倾斜入射角,整个光学系统的数值孔径(NA)就比较难极大化,目前的EUV其NA=0.33,与DUV的NA可以高达1.3存在巨大的差距。而数值孔径与分辨率成正比。这是个关键的光学特性。

由于目前EUV波长已经一口气推进到接近X-ray波长的上限,再要缩短波长恐怕要用新的物理机制产生新的光源 , 那这将又是另一段20年艰苦的研发旅程, 所以目前整个产业界的努力都集中2个面向,增加NA和增加产出,比如ASML近期即将交付Intel的0.55 High-NA EUV光刻机。

以目前13.5nm波长的EUV大概能做到哪个技术节点?

这点是整个半导体产业共同关心的问题。早在2000年代行业讨论DUV之后的曝光机光源时,当时已有摩尔定律已日暮的感觉,可是最后却又奋力推进这么多年,直到EUV接手 , 20多年前谁都想象不到未来可以发展出这样的技术来延续摩尔定律。

理论上,一个光源的分辨率大概在光源的半波长(Half-Pitch)。譬如第二代DUV ArF的波长是193nm,理论分辨率就只有96.5nm。但是透过多重曝光(multiple exposure)、过刻(over etch)、相位移(phase shift)以及浸没(immersion)在水中改变光的折射率等工程手段,193 nm DUV目前可以处理到7nm的节点,如果不计代价 , 也可以到达浸没式发明者林本坚博士所说的5nm甚至更低 , 国内许多自媒体宣称所谓28nm光刻机无法做到7nm很显然是有误 , 甚至90nm光刻机能不能做到28nm这问题 , 其实理论上 , 不在意生产成本是可以达成 , 因为这并非只是光刻机本身极限的问题 , 而是许多配套工艺以及成本的问题。

而波长13.5nm的EUV可以推进到哪一个技术节点?

要注意的是现在逻辑制程的节点与早年以晶体管实际的栅级长度(Gate length)为命名已有所有不同,7、5nm的栅级长度超出10nm不少。目前节点是以1个晶体的总体表现,如速度、功率、热耗散、面积等综合因素来命名,最直观的方式就是比较单位晶体管密度MTr/mm2。

如果最小结构装置仍然以硅晶为基础、以电磁学为控制手段,那么硅基元件的最小尺寸是可以粗估的。硅的共价键长度为0.111 nm。要组织一个元件的功能部分 , 譬如沟道就至少要有几十个原子的内部,要不然物质表面的性质可能就会影响物质内部应有的性质,因而影响元器件的特性 , 最明显的就是我们经常看到的遂穿效应造成的漏电。几十个的硅原子就是小几nm的长度了,已经接近现有的EUV的理论分辨率,这也是当初产业界一口气将光源波长从193nm推进至13.5 nm的考虑。

如果对原分子的控制可以更精细、物质的表面性质可以被精确掌控,比如目前行业正大力研发的2D材料 , 因而使用较少的硅原子也可以构成有效元件,这时在半导体制程演化至物理的自然极限前,光源的波长还留有一个小窗口,这个窗口的候选人就是同步辐射与自由电子的光。

(编者按:其实目前行业并非完全依赖纯微影(Litho)技术来推进线宽的缩小 , 多曝这种可以有效降低k1值的RET增益手段 , 让DUVi可以从45nm推进至7nm甚至5nm 共6个节点 , 理论上这在EUV上也同样可以达成 , 当然这是一个复杂的问题 , 主要还是在成本平衡的问题 , 简单说 , 目前波长13.5nm的low-NA EUV未来面对2nm甚至1.4nm的Half-MP还是有冗余的)

同步辐射

同步辐射所产生的光,是由电场加速带电粒子因而产生辐射产生的光,不像激光是利用原子天然能阶之间的跃迁产生的相干光(coherent light),光源波长是可以控制、设计的。

同步辐射产生光的波长,从远红外至hard X-ray,大约是10nm到0.01nm, 虽然很难达到理论最小值 , 但这波段已足以处理硅基半导体制程的所有波长需求。

高于DUV波长的光就不必讨论了 , 毕竟DUV是既有成熟的设备,不必再重新发明轮子。可以讨论的是现在EUV波长波段,以及将硅基半导体推向物理极限的几nm波长的光。

用同步辐射做为光源有个明显好处,即为光的亮度充分。只要加速器中心能稳定控制的电流够大,就是电子够多, 辐射光的亮度便充分,这样就可以立刻解决现在EUV产量上亮度不够好的窘境,这也是去年炒作同步辐射当光刻机光源的理论依据。

同步辐射光源也面临现在EUV因光的能量较高,容易被物质吸收的问题,如果波长更短,问题愈严重,物镜系统是EUV的难点这也同样是同步辐射的难点,而去年炒作同步辐射的小作文却离谱的宣称同步辐射不用复杂的物镜系统。

同步辐射正在使用的光学元件, 也不是甚么新鲜技术路线。但是同步辐射是仪器(instrument),而光刻机是量产设备(equipment),二者要求的精度、可靠性、成本等有巨大差距。

除了物镜系统、精度、可靠性、成本等难点以外,同步辐射要做为光刻光源还有另外的2个大挑战。

同步辐射基本上是个圆形加速器,出光口散布在圆周外围,这个格局与现在的晶圆厂的布局(layout)天差地别。如果使用同步辐射,会大幅更动晶圆厂的运作方式,甚至是一些界面规格,作者作为一个资深的Fab建厂工程师 , 我第一个想到的就是如此庞大的装置如何保证Particle这个Clean room最惧怕的污染物 , 这是影响芯片良率的一大要因。

EUV虽然体积也不小,但是长的方方正正的,放在Fab合适而且每部机台独立运作互相不干扰,这也是当初半导体产业选择使用现在EUV的理由之一。不过产业界做过评估 , 下一代的High-NA EUV可能是Fab能容纳的极限 , 因为文章前面提到的倾斜入射角的原因 , High-NA物镜就会变得异常庞大 , 这几乎到达Fab现有技术允许的上限 , 未来还有Hyper -NA这需要接近30米高的庞然大物将使得Clean room的管理与建造要求出现全新的变化。

同步辐射的第二个挑战是维修时的停机时间(downtime)。设备维修,停机理所当然。但是同步辐射加速器的维修会导致每个出光口同时停机,晶圆厂就处于完全停产状况。

在半导体产业眼中,这是只有在灾难时才会出现的状况。

半导体产业的逻辑一般是将既存的技术和设备榨出最后一滴价值,最大幅度的降低设备折旧与技术摊提。所以现在光刻机的发展主流是尽其所能的提高EUV的亮度以及分辨率,并且佐以其他非曝光手段如奈米压印与定向自组装(DSA)等方法,以期能够支撑到硅基精细元件的物理极限。

单纯从微影技术来看 , 同步辐射相较于目前的EUV来说,理论极限只能推进2~3个节点,毕竟光源波长只是10nm与1nm的区别,在文章之前也提到目前产业界都是多种手段来缩小线宽,光刻只是其中之一,而多重曝光以及过刻、相位移等技术都比单纯的提高光刻极限来的容易,目前行业正在发展的其他非曝光手段如奈米压印与定向自组装(DSA)等方法,台积电与Intel都在这些技术上布署重兵攻关 , 台湾省的台大,交大与清华都有针对DAS技术的课题组 , 全部均由台积电提供大量资金与合作。

进入AI时代 , 半导体行业也走在前端 , 台积电,ASML与NV三方合作利用AI打造的cuLitho计划 , 新加入了EDA巨头新思 , cuLitho从去年一直在进化当中 , 未来对半导体制程也将有重大的影响。

另外之前网传的清华光刻厂,计划建设KW级别光源,其实ASML目前的High-NA EUV光刻机EXE5200就已经达到600W,这也才是一台EUV的功率,所谓KW的同步辐射光源可能还没有两台EUV产能来的高,所以光刻厂至少是要100KW或者MW级别,同步辐射要产生100KW级别的光源,个人认为技术还有很远的路要走而且建设资金也并非网传同步辐射不贵,小装置确实不贵,但小装置不如一台EUV,要达到光刻厂的功率那将是天文数字,另外还得搭配一座专用的小型核电站。

综合上述原因全球半导体产业界打造同步辐射来取代EUV光源的动力很显然是不足甚至没必要, 因为其潜在竞争力并没有大幅超前其所需要投入的成本,但同步辐射在中国引起广泛讨论的跟根本原因是我们被西方限制无法取得先进光刻机,急需另起炉灶以实现弯道超车。

但这或许是国内无良自媒体的又一次炒作,如文前所述,40年前我国中科院高能所早就构建起第一代的同步辐射装置,同时90年代初期全球半导体产业对下一代光刻机的光源的探讨,就包括了同步辐射光源、自由电子激光器、放电等离子体(DPP)光源、和激光等离子体(LPP)光源,经历可写成一本书的千辛万苦, 近20年的努力最终ASML代表的LPP路线胜出,所以清华同步辐射的光刻厂,不就是对30年前全球产业界早已经论证完成的技术路线又一次冷饭新炒。

其实目前清华大学并没有实现SSMB光源,他们只是在2021年对一个加速器新理论的试验工作发表了一篇论文,并获得Nature刊登。

这个技术最初就是由美国劳伦斯伯克利国家实验室的华裔科学家赵午博士提出,赵午博士在台湾出生,台湾清华毕业后到史坦福进行加速器理论研究,2017年退休后成为北京清华的访问学者,经由赵博士牵线并与清华的唐传祥研究组合作,最后由清华大学、赫姆霍兹柏林材料研究中心(HZB)与德国德国联邦物理技术研究院(PTB)的合作团队在德国的同步辐射装置开展的早期验证试验成功并于Nature发表研究成果,也是基于这个研究成果,清华开始建设雄安SSMB EUV装置。

我们期待怀柔的第四代同步辐射装置与清华SSMB EUV有朝一日能顺利点亮,即便它还只是一个初步的验证装置,未来SSMB成功点亮的一天我们才需要来考虑其作为光刻机可能性的各项工程细节探讨,SSMB作为可用的光刻机光源确实还有点太早 , 但如文前所言被西方限制的中国半导体行业该怎办?最近有点火的纳米压印技术又如何呢?

奈米压印

奈米压印的方法其实很简单,就像用活字印刷将木模板转印图案到纸上一样。

木模板是阴刻,1:1的将字的图案压在纸上,利用颜料最终在纸上显示出图案 , 压印后的图案是阳刻的。这过程没有像光刻程序中牵涉到光源、光学系统、感光、显影、蚀刻等复杂的过程以及精密昂贵的设备,所以晶圆处理程序价格相对较低似乎是理所当然。

关键的技术是压印模板的制造,以及前文中以颜料比拟的高分子树脂及整个压印过程。压印模板与欲转印的图型是1:1,所以在制造模板时要有至少与在晶圆上欲转印的图案一样精细的分辨率,这用来塑造模板图样的工具自然是电子束(e-beam)。电子束是半导体业用来在掩模板上形塑线路图样的主要工具。

电子的德布罗意(de Broglie)波长是0.08nm,也就是说电子束理论上的分辨率就是在这数量级。对于任何目的的刻画,这都远超过所需要的精度!

问题是被电子束用来呈像的物质会与电子发生作用,因此电子束刻画的分辨率极大程度的依赖于使用的物质。目前电子束的分辨率大约在5~10nm左右,这对于5nm制程实际的临界尺寸14nm便够了。奈米压印还预告未来可以推进到2nm制程节点,2nm实际的临界尺寸是8~10nm,也还在目前电子束分辨率可触及的范围之内。

以电子束刻画的掩模版是母板(master plate),接下来就是大量复制。说「大量」一点也不夸张,因为目前佳能推出的奈米压印机每小时产量就只有100片上下,100的WPH这比EUV的Alpha机器都还要低更别说量产机型,以现有技术来看掩模板可以使用的次数在几千次的数量级,因此我们清楚经过2-3天掩模板就得更换,所以在纳米压印技术中掩模板的成本将非常高。

在奈米压印之前,基板需先滴有高分子树脂,与基板上粘合层充分浸润。之后就是将模板压在布满高分子树脂的晶圆,藉压力及毛细现象让树脂延伸入模板图形之中。然后用紫外光固化(UV curing)树脂,取下模板。

奈米压印过去技术发展的挑战和上述的压印过程和使用的物质有直接的关系。过去的几大挑战分别为套刻(overlay)、产量、缺陷率(defectivity)和微颗粒。

套刻是指元器件上下不同层间结构的对齐问题,在奈米压印制程中会产生覆盖问题的原因之一是压印过程中树脂被压印而扭曲或变形,以致于上下层之间的相应结构无法对齐,这是奈米压印过去在技术上常被诟病的地方。

又譬如奈米压印的产量其实取决于树脂滴(resist drop)的大小、扩散速度以及跟基板粘合层的浸润速度,这些问题基本上是材料特性的问题。

这些问题在过去发展的30余年间主要由材料的改善以及一些辅助的机制,譬如上下层对准校正等,这些问题获得相当程度的改善,奈米压印因而逐渐步入量产制程的行列。

最近佳能热炒的FPA-1200NZ2C奈米压印机这个型号,其实最早在2015就已出现在相关的学术期刊上了。

已经出现8年的旧机型能够重新引起业界广泛的注意,最主要的原因在于它将要进入比较大范围的半导体量产应用。

奈米压印有2个特性可以有效地拓展它的应用范围。

第一,是它不仅适用于2D图形,有些3D图形也可以用单一掩模板来转移线路图形,这可以有效的简化制程。另外一个特性,是奈米压印可以用于任何基板,不只是适用于硅晶圆上。

这2个特性让奈米压印已经开始被应用于一些次领域,譬如生物传感器等MEMS领域。只是这些领域的产值相对较小,并未获得充分关注。

这次佳能纳米压印受到较多关注的原因,是奈米压印要进入主流半导体制程行列,而且时程明确。

铠侠(Kioxia)与SK海力士将于2025年开始,以奈米压印技术生产3D NAND Flash。NAND在很长一段时间内是市占率仅次于DRAM的半导体产品类别,奈米压印进入大宗产品的制程行列,意义非凡。

东芝(Toshiba)于2004年就开始跟佳能合作以奈米压印试产NAND,目前铠侠与佳能和Dai Nippon等公司为共同推动建立奈米压印技术生态的主力成员。SK海力士身为铠侠的股东与铠侠一直以来就有市场与技术合作,同时宣布采用奈米压印技术也在情理之中。

NAND可以率先采用奈米压印有其技术上的理由:NAND是存储阵列。

与高度客制化的逻辑芯片不同, 一般存储阵列线路图形高度重复,基础单元结构相对简单。最重要的是其容量设计可以留有冗余(redundancy),如果制造过程中有局部线路图形产生缺陷,可以用硬件方法融断受损部分,用原先预留的冗余部分替代,晶圆整体良率可以维持在较高水平。

如果奈米压印要应用到DRAM,缺陷密度的要求也一样可以较为宽容。但是DRAM底部晶体管触点太过密集,因此上下层间的对准就变得格外重要,以前奈米压印的技术规格尚达不到量产的要求,需要再改善套刻精度后才谈得到DRAM的应用。

至于逻辑芯片,由于线路中大多不是重复的图形,比较少有冗余设计的可能,对于颗粒物或缺陷极为敏感。目前的奈米微影机仍需降低颗粒污染和缺陷才有办法跨入逻辑芯片的制造应用。

另一个比较有期待的领域是硅光。

奈米压印在转印线路图形时的线边缘粗糙度的表现优于传统光刻机的表现,因为没有光的干涉、光阻蚀刻等问题,这使得光子在通过这些以奈米压印制造的光元件时,表现更符合原设计的预期效能,而且一般光学元件制造层数较少,层间覆盖的问题没有那么尖锐。另外,光学元件很多是3D图形的,这正是奈米压印的强项之一。

硅光还有另外一个机缘。早先业界对异质整合路线图(HIR)就计划于2020年硅光出现在异质整合芯片市场中,但是实际上被延迟了。2023年由于人工智能(AI)应用的兴起,大量资料移动的需求要以光的形式来实现,硅光被正式推上台面 , 台积电就宣布在2025年开始硅光的量产。

半导体产业的逻辑,总是会将机器设备的价值利用到最后一刻,毕竟原始的投资太过巨大,所以对新设备的引进就有潜在的使用障碍。

但是这些原本半导体产业的逻辑却不太符合我们实际国情,中国有所谓举国之力,让我们可以不畏前期巨大的投入,国家无穷无尽的补贴,让行业可以无序生产把海外竞争者挤出赛道,诸如钢铁 , 化工 , 光伏与液晶面板。

我们原本屡试不爽依靠国家强力补贴的发展模式却在半导体这个领域无法发会综效,主要原因还是半导体产业鍊着实太长太庞大,每个细分领域都是全球顶尖,每个细分领域都需要突破,短期内依靠国家补贴确实很难出成绩,这是一个需要长期积累的行业。

相对于同步辐射,纳米压印已被证明可以实现并有具体落地应用,但纳米压印与传统半导体制程中的光刻完全不一样,配套的刻蚀薄膜沉积等关键设备也会有很大的不同,这将改变由来已久的半导体制程供应链,整个体系都需要重整,如此看来,这不正好符合具备举国体制这种不怕耗费巨资又不担心原本供应链打掉重练的中国吗?

对于被限制先进光刻机取的中国,我们是否应该被迫转移新的技术路线,还是坚守传统西方光刻机路线?

结论

其实答案并非一体两面 , 而是要适合国情 , 文章前半段已经说明了同步辐射早在几十年前行业的技术论证中就败下阵 , 纯属冷饭热炒 , 目前也压根不具备成为制造芯片的光源的选项 , 而EUV对于未来芯片推进至1nm节点以下 , 配合其他技术还有很大的挖掘空间 , 所以EUV理所当然是最优选项 , 但无奈西方对我国的技术封锁 , 无法取得。

那用DUVi继续探索5nm甚至3nm成了目前我国半导体迫在眉睫的唯一选项 , 实际上国际半导体行业也早就在进行这些技术的开发 , 因为这些增益技术不只是在DUV上使用也同时可以在EUV上发光发热 , 无奈我国半导体技术积累不足 , 对于全球行业新技术路线投入也不足 , 前沿的DAS定向自组装 , ILT反演光刻 , IMEC在去年就发布了DUVi SAOP(八重曝光) , 并和Mentor共同创建不需添加任何冗余金属 , 没有额外的电容SALELE(自对准-光刻-刻蚀) 全部都是DUVi可以用来制作5/3nm甚至更先进芯片的技术 , 很可惜的是2024年我们只看到某大厂发布了一个SAQP专利 , 这是行业7年前已经用来生产芯片的既有技术 , 对于更新的前沿技术作者几乎没有发现国内有相关布署 , 作者认为从高校,科研机构以及国内各大厂在研发光刻机的同时也要重点投入这些行业已经确定的前沿技术 , 不要整天只知道光刻机 , 明明有许多技术同样可以突破西方封锁 , 持续推进我国芯片的先进节点 , 难道只因为研发光刻机的项目好拿钱就一股脑全投入在这 , 或者它有某些政治意义?

纳米压印也是一个不错的方向 , 作者认为即便纳米压印目前还有诸多缺点不成熟 , 但如果搭配DUVi只让纳米压印去压印极少数的Key layer那可发挥奇效 , 因为纳米压印利用e-beam刻掩膜有非常高的精度 , 只刻少数Key layer正好避开的纳米压印的重大缺点(没法一直高强度大量压印并保持高精度) , 而且纳米压印具备的3D图形压印是传统光刻机所不具备 , 这正好是未来存储芯片以及硅光所需要的 , 这不都是我国半导体极力想突破的问题点。

全球半导体行业有无数研发工程师在竭尽脑汁想办法推进摩尔定律 , 压根没有国内舆论大行其道的摩尔定律到2nm或多少nm就会停止不前我们将有大把时间追赶的说法 , 從2024始可以确定的20年内 , 芯片晶体管的密度跟总数将持续快速增长 , 甚至在单芯片功耗上超越原本的摩尔定律 , 比如3月份台积电的刘德音与黄汉森在IEEE发表的文章 , 计算出不用十年 , 人类就可以制造出一万亿颗晶体管的GPU单芯片 , 未来不再是只通过制程改善缩小线宽这单一手段来提升晶体管数量 , 立体结构的优化、2D新材料以及先进封装每一个技术都能有效并持续的提升晶体管数量。

摩尔定律将停止 , 我们将会有很多时间追赶西方的说法纯属自欺欺人 , 或者懂的人欺骗领导或无知网民的说法。既然未来中国半导体还有那么长的路要走 , 必然对于全球先进技术我们也要同步发展 , 不需要急功近利只图一个光刻机 , 因为今天这篇文章让大家知道了未来还有那么多技术路线可以突破封锁 , 多点布局多条腿同时走路 , 是我们中国发展任何产业的强项 , 只要不被利益团体蒙蔽不被忽悠 , 看好方向选对路线 , 中国半导体必然可以崛起。