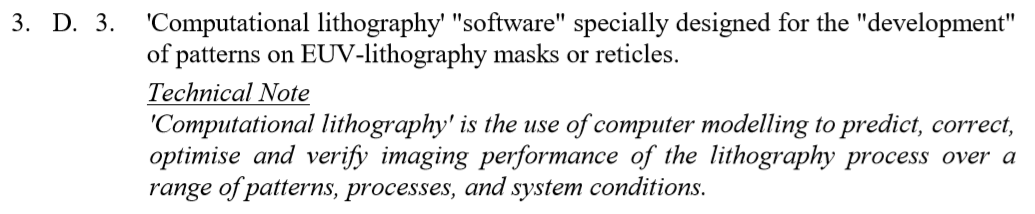

2019年最新版“瓦森纳安排Wassenaar Arrangement”的“军民两用技术清单”中,在2018年版的基础上,将原“物理模拟软件Physics-based simulation software”修改为“计算光刻软件Computational lithography software”。

2018年版的内容表述为:物理模拟软件

2019年版的内容直接表述为:计算光刻软件。

芯思想研究院对历年“瓦森纳安排”的“军民两用技术清单”进行了仔细研读后发现,针对这一条款,在“瓦森纳安排”24年的历史中,经过两次修订,第一次修订是2003年版,将最初的“计算机辅助设计软件Computer-aided-design(CAD)software”修订为“物理模拟软件Physics-based simulation software”。

芯思想研究院认为,这一条款修订非常关键,每次修订都将范围扩大,而且这次修订特别指明极紫外光(ExtremeUltra-violet,EUV)光刻,直接击打在中国半导体光刻工艺研发的七寸上。

光刻(lithography)是集成电路制造中最重要的步骤,是目前最主要的在晶圆上制作亚微米和纳米精度图形的技术。光刻是利用光化学反应(Photo-Chemical Reaction,PCR)原理把制备在掩模上的图形通过光刻投影系统转印至晶圆上的过程。光照射在掩模上发生衍射,衍射级被投影透镜收集并会聚在光刻胶表面,这一成像过程是一个光学过程;投影在光刻胶上的图像激发光化学反应,烘烤后导致光刻胶局部可溶于显影液,这是化学过程。如此说来,光刻包括光学和化学过程。

计算光刻技术其实就是利用软件和高性能计算,来模拟仿真光刻过程中的光学和化学过程,或者说是模拟光学邻近效应修正(Optical Proximity Correction,OPC),从理论上探索增大最小可分辨特征尺寸(Minimum Resolvable Feature size,MRF)和工艺窗口(Process Window,PW)的途径,指导工艺参数的优化。

要了解计算光刻技术的意义,我们要先了解一下有关光刻投影系统的几个概念。

1、光刻投影系统的最小可分辨特征尺寸(Minimum Resolvable Feature size,MRF)

投射到晶圆上的特征图的精度,取决于投影系统的光波长,以及经过光掩模板(illuminated mask)衍射光的衍射级次有多少能被投影透镜系统(ProjectionOpticalSystem)捕获。当前最常用的光刻投影系统使用的深紫外光(Deep Ultra-violet,DUV)是由波长为248nm和193nm的准分子激光器产生的。但是先进制造工艺已经进展到了7纳米和5纳米,这些工艺使用的极紫外光(EUV)是由波长13.5nm的激光器产生的。

光刻投影系统能够刻印的最小可分辨特征尺寸(Minimum Resolvable Feature size,MRF)的计算公式如下:

MRF=曝光光源波长(λ)* k1/NA

*k1是一个独立于光学成像的因子,取决于光刻投影系统和光刻胶的性质等因素,通常为一个0.25-1之间的常数(从1996年至今,最初是0.7,也有过0.4,现在是0.35)

*NA是投影镜头的数值孔径(Numerical Aperture,NA)

通过这个公式,我们可以看到MRF与λ是成正比的,与NA成反比的。要提高MRF,可以减小曝光光源波长λ,增大数值孔径NA。当掩模版图形尺寸远大于光源波长λ, 亦即远大于MRF时,由衍射产生的图形偏差可以忽略不计,在这种情况下光刻胶膜中通过曝光形成的光刻图形与掩模版图形基本相同。然而由于技术发展和资金规模的限制,光刻投影系统所用光源波长的减小速度远远慢于电路特征尺寸的减小速度。

这样我们就可以理解ASML的EUV光刻投影系统要加大NA,目前NEX:3400C的NA是0.33,ASML正在和Carl Zeiss(卡尔蔡司)努力将NA提升至0.55,以装备在EXE:5000光刻投影系统中,如果完成,MRF将缩小30%,工艺进展可至3纳米。

2、光刻投影系统可清晰成像的尺度范围/焦深(Depth of Focus,DoF)

由于晶圆平整度误差、光刻胶厚度不均匀、调焦误差以及视场弯曲等因素的存在,最佳成像平面与实际成像平面之间总是存在一定误差,这被称之为离焦。离焦一般会导致成像质量下降,并且由于光刻胶层有一定的厚度,要保证蚀刻质量也要求其上下表面的成像有一定的一致性。这都要求成像系统能够保证在理想成像平面上下一定范围之内都有较佳的成像效果。一般将这一范围称之为焦深(Depth of Focus,DoF)。简单地说,就是在芯片表面最高处和最低处都必须达到分辨率的要求。

焦深可以通过下面的公式计算:

DoF=曝光光源波长(λ)* k2/NA2

*NA是投影镜头的数值孔径(Numerical Aperture)

*k2因子随照明方式的不同而变化,理论上可以大于1

通过这个公式,我们可以看到DoF与λ是成正比的,与NA成反比的。要提高DoF,可以增加光源波长λ,减小数值孔径NA。

那么问题来了,MRF是越小越好,DoF则是越大越好。因此通过减小光源波长λ以及增大NA的方法,在提高分辨率的同时,也会降低系统的焦深,两者是矛盾的。所以增加NA要和DoF折中考虑。

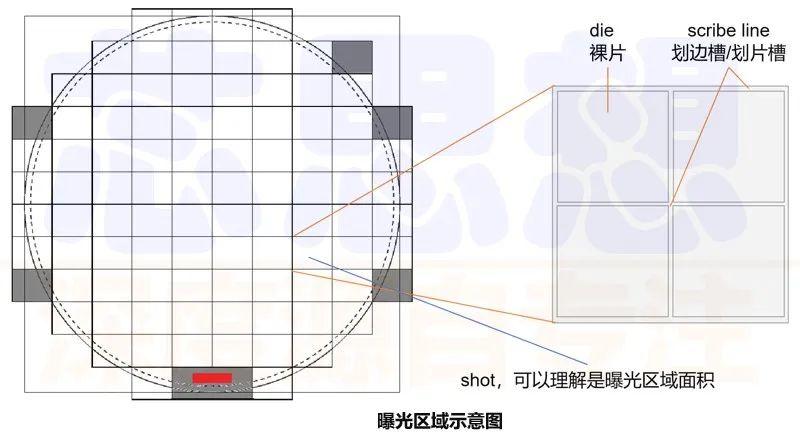

专家还对笔者表示,设计曝光系统时还需要折中考虑曝光区域(exposure field)。曝光区域越小,就需要更多的时间来完成整片晶圆的曝光。

3、曝光区域(exposure field)

在光刻工艺中,光刻投影系统单次实现曝光所能支持的最大区域范围为曝光区域。先进步进扫描式(Scanner)光刻投影系统所能支持的最大曝光区域面积是26mm×33mm,目前ASML的最先进的光刻投影系统TWINSCAN NXE:3400C就是这个曝光区域;而步进式光刻投影系统(Stepper)的曝光区域只有22mm×22mm,不过2019年12月佳能(Canon)发布的i线步进式光刻投影系统FPA-3030iWa的曝光区域可达52mmx52mm。

事实上,光刻工艺中,在曝光时,实际芯片可能小于这个尺寸,光刻投影系统的曝光区域必须能够随之做调整。也可以把几个不同的版图放在同一张掩模版上,这样一个曝光区域中就可以有几个不同的器件设计(die),最终制造成几个不同功能的芯片。

随着工艺的不断进步,设计尺寸不断缩小,器件中最小线宽开始小于曝光波长,越来越逼近光刻投影系统的极限,光的衍射效应变得越来越明显,导致最终对设计图形产生光学影像退化,实际形成的光刻图案相对于掩模版上的图案发生严重畸变,比如晶圆表面成像相对于原始版图会出现拐角处圆化、线端缩短、线条宽度变窄等严重的不一致,最终在硅片上经过光刻形成的实际图形和设计图形不同,这种现象称为光学邻近效应(Optical Proximity Effect,OPE)。

我们知道,摩尔定律的推动下,为了更高的性能,更低的功耗以及更低的成本,用于光刻的光源波长从436nm(g线,汞灯),405nm(h线,汞灯),365nm(i线,汞灯),248nm(DUV,KrF准分子激光),193nm(DUV,ArF准分子激光),到目前最先进的13.5nm(EUV)。也就是说当MRF进入0.5μm以下时,MRF和光源波长一直存在间隔,且一直在扩大,掩模图形和晶圆表面实际印刷图形之间的光学邻近效应越发明显 ,就要开始进行图形修正。

事实上,在0.5μm以下的工艺中,从i线到深紫外线,由于DoF的要求,业界提出并广泛采用了在不改变光刻波长的前提下通过控制光刻投影系统的其他各项参数,如减小k1或增大k2(使用NA可变的镜头),来实现提高图形转移质量;还有就是采用减小光刻畸变和提高系统焦深的分辨率增强技术(Resolution Enhancement Technology,RET)。目前业界把这些技术统称计算光刻技术。

具体来说,计算光刻技术包括光学邻近效应校正(Optical Proximity Correction,OPC)、光源-掩模协同优化技术(Source Mask Optimization,SMO)、多重图形技术(MultiPatterning Technology,MPT)、反演光刻技术(Inverse Lithography Technique,ILT)、离轴照明(Off Axis Illumination,OAI)、亚分辨率辅助图形(Sub-Resolution Assist Feature,SRAF),也包括有效填补(dummy fill)、工艺变化带宽(Process Variationband,PV-band)分析、边缘放置误差(Edge Placement Error,EPE)改善。

现在,在先进工艺特别是FinFET工艺中,计算光刻已经成为光刻工艺研发的核心。计算光刻是依靠专用EDA(电子设计自动化,Electronics Design Automation)工具来实现的,这些EDA工具都是有专门的供应商提供的。

下面我们简单介绍一下几大计算光刻技术的情况。

光学邻近效应修正(Optical Proximity Correction,OPC)

前文提到,在光刻过程中会产生光学邻近效应,为了修正光学邻近效应,便产生了光学邻近效应修正技术。随着工艺的进一步发展,光学临近效应修正已经成为光刻图形处理的关键步骤,变得必不可少。

光学邻近效应校正可以算是最早的计算光刻技术。前文说到,当晶圆上的线宽小于曝光波长时,必须对掩模上的图形做光学邻近效应修正。光学邻近效应修正中应用了一种被称为图像分割(Fracturing)的技术,将需要成像的图形划分成许多小块,并且利用衍射光束之间的相互干涉效应,在掩模板上将需要成像的图形的形状进行一些改变,并在转角等处添加或减少一些小块图形,这样就可以利用衍射效应来消除最终在晶圆上成型的图像转角等边缘处可能出现的图像边缘缺陷。

光学邻近效应校正有两种,一是早期基于规则的OPC(Rule-Based OPC,RB-OPC),二是现在基于模型的OPC(Model-Based OPC,MB-OPC)。

RB-OPC首先于0.25μm技术节点被引入光刻工艺中,由于其简单和计算快速的特点被广泛使用。然而这种方法需要人为制定OPC规则,OPC软件根据事先确定的规则对设计图形做光学邻近效应修正。这种方法的关键是修正规则,它规定了如何对各种曝光图形进行修正。其形式与内容会极大的影响OPC数据处理的效率和修正的精度。修正规则是从大量实验数据中归纳出来的,随着计算技术的发展,修正规则也可以通过计算的方法产生。修正规则都是在一定照明条件下产生的。如果工艺条件发生了变化,这些修正规则必须重新修订[1][2][3]。

随着光学畸变加剧,这些规则变得极为庞杂而难以延续,必须在结合RB-OPC的情况下引入MB-OPC,并让MB-OPC承担主要的修正职责。

MB-OPC从90nm技术节点开始被广泛应用,使用光学模型和光刻胶化学反应模型来计算出曝光后的图形。MB-OPC通过光学仿真建立精确的计算模型,然后调整图形的边沿不断仿真迭代,直到逼近目标图形。

MB-OPC的流程更加复杂,对计算资源的需求呈指数级别增长。光刻工程师还使用一些专用的测试图形曝光,收集晶圆上的数据,用来修正软件里的模型,使之计算出的结果和实际尽量吻合。显然实验数据越多,模型拟合越精确。但是太多的测试图形会使得晶圆数据的收集量太大。因此,测试图形的设计非常关键[1][2][3]。

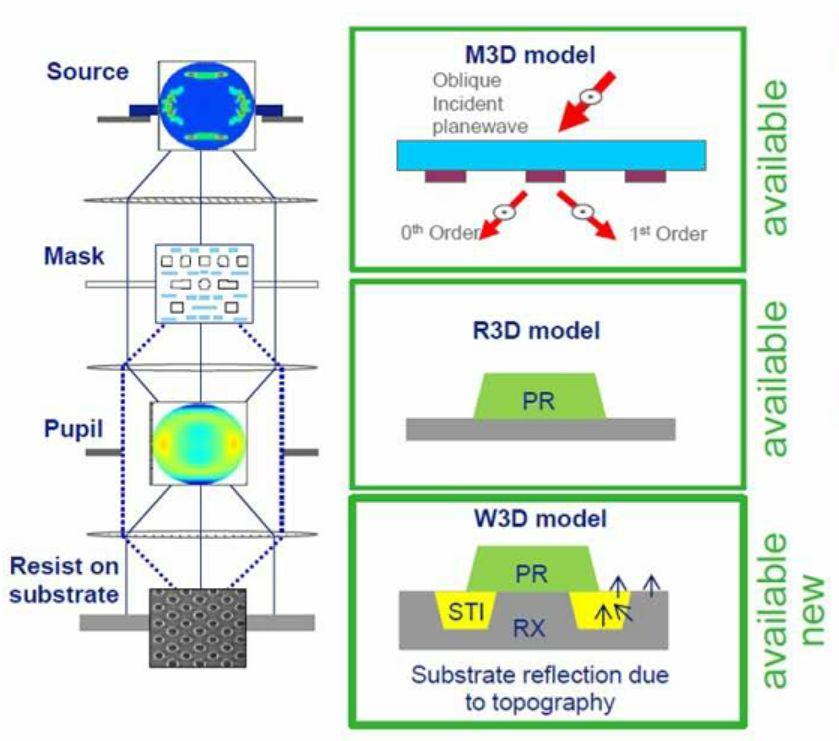

随着器件尺寸向10nm以下发展,各种不常见的物理现象层出不穷。例如从掩模表面散射的电磁波需要更严格地建模(Mask 3D效应),以表示掩模版表面立体结构对光衍射的影响。OPC工程师不仅要考虑光学畸变,还要考虑光刻胶工艺(Resist 3D效应)的影响,例如烘烤和显影。这时的OPC已经不再是单纯的数据处理,而是综合考虑物理、化学、光学、高性能计算的跨学科应用,使得实现OPC的EDA工具也非常复杂。此时,工程师的经验在计算光刻解决方案部署过程中起非常关键的作用,它们将决定解决方案的效能和效率,进而影响到整个节点工艺的成败。

说到底,光学临近效应修正技术就是掩模优化(MaskOptimization,MO),根据已定的光源,通过修正掩模形状来改善图形的光学表现。

多重图形技术(MultiPatterning Technology,MPT)

前文提到,由于工艺制程的提升,最小可分辨特征尺寸(MRF)已经远远小于光源波长,利用DUV曝光系统已经无法一次刻蚀成型。

既然无法一次刻蚀成型,那就多刻蚀几次,每一次刻蚀一部分,然后拼凑成最终图案。于是业界提出了多重图形技术。目前有两种实现方式,一是曝光-刻蚀-曝光-刻蚀(Litho Etch Litho Etch,LELE),二是自对准多重曝光技术(Self-Aligned MultiPatterning,SAMP)。

LELE是将设计版图分解成两套独立的低密度图形,通过两次单独曝光和两次单独刻蚀,然后叠加在一起,形成更精细的图案。但是LELE要求设计人员对版图做拆分,即所谓的分配颜色,把原始绘制的版图拆分到两块掩模上。在LELE工艺中,后续曝光时必须对先前的图形进行结构保护;更大的难题是两次光刻的对准问题。目前LELE工艺已经被广泛应用于14nm及以下技术节点的器件中。目前LELE已经演变成TPT LELELE(Triple Patterning Pattern spiltLitho Etch Litho Etch Litho Etch)。

SAMP是通过一次光刻形成核心图形,然后通过沉积(Deposition)在核心图案两侧形成侧墙(Side Wall),最后通过刻蚀(Etch)和修剪曝光来实现所要的图形。SAMP已经从SADP(Self-Aligned Double Patterning)演变出自对准三重曝光技术(Self-Aligned Triple Patterning,SATP)和自对准四重曝光技术(Self-Aligned Quad Patterning,SAQP)。SAMP工艺已经被广泛应用于FinFET的制造中。

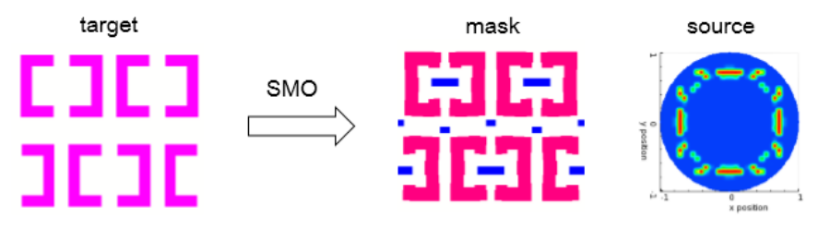

光源掩模协同优化技术(Source Mask Optimization,SMO)

前文提到,OPC是根据已定光源对掩模进行优化,增大工艺窗口。对于28nm及以上技术节点,最常用的照明光源是固定形状的,例如环型(Annular)、双极型(Dipole)、四极型(Quasar)等。

随着工艺节点的不断推进,现在已经来到20nm,且更先进的已经进入10nm以下,pitch越来越小,对分辨率的要求越来越高,已经逼近了193nm浸没式光刻技术所能达到的极限,常规照明方式下使用OPC无法获得足够的工艺窗口,就需要光源上光强分布尽量集中。于是光源优化(Source Optimization,SO)概念应运而生。

SMO技术出现于2000年,是一种针对极小尺寸图形光刻的计算光刻技术,对光刻工艺中的光源和掩模进行协同优化,来改善在超小尺寸节点中的光刻工艺窗口,增强光学表现。很快SMO技术就获得大范围应用。

光源优化通过针对具体出现的多类图形,如实际版图中的不同pitch的line & space和line end以及C型dipole等各类图形,对光源的形状进行修饰,形成定制形状的光源,使之能够照顾到绝大多数图形和最关键的图形,获得较好的工艺窗口。

光源形状和掩模形状对工艺窗口的影响并不是相互独立,将以上的MO和SO的概念结合在一起,对光源和掩模进行协同优化,便是SMO所做的工作,即根据给定的光刻条件和实际版图,通过SMO给出优化后光源和与之对应的掩模板图形,虽然掩模板图形并不能作为最终OPC的结果,但可以为OPC的工作提供一定的参考。

典型的SMO

SMO除了优化光源,提升光刻的工艺窗口外,还可以为design rule(设计规则)的制定提供依据。

反演光刻技术(Inverse Lithography Technology,ILT)

反演光刻技术(Inverse Lithography Technology,ILT),是以晶圆上要实现的图形为目标,反演计算出掩模版上所需要图形的算法。就是将光学邻近效应校正(OPC)或光源-掩模交互优化(SMO)的过程看做作为逆向处理的问题,将光刻后的目标图形设为理想的成像结果,根据已知成像结果,根据投影系统空间像的变换模型,反演计算出掩模图像[4]。

反演光刻技术能够使光刻掩模图像获得最大的自由度。结合光刻掩模技术的发展,反演光刻技术提供单次曝光所能获得解析度的极限。

虽然ILT和OPC的目的是完全一样的,使曝光后晶圆上的图形和设计图形一致,但是其方法却有着完全不同的思路。相较OPC需要事先进行切割,ILT是对整个版图进行离散化处理。

ILT不仅是对设计图形做修正以期在晶圆上得到所要的图形,而是把要在晶圆上实现的图形作为目标反演计算出在掩模上所需要的图形。反演光刻通过复杂的数学计算得到一个理想的掩模图形。用这种方法设计出的掩模,在曝光时能提供比较高的成像对比度[1]。

由于反演光刻技术非常复杂,特别是对整个芯片而言计算量很大,所以从2005年Luminescent Technologies(2014年被KLA收购)推出第一套可商用反演光刻软件以来,业界认为在在整个芯片布局中使用ILT是不切实际的。

目前普遍的做法是先使用通常的模型修正(OPC+SRAF)来完成掩模数据的处理,然后找出其中不符合要求的部分,也称为“坏点”。把这些“坏点”截取出来,局部做ILT处理,得到最佳的修正。最后再把经ILT处理后的部分贴回到数据中去。这种局部的ILT处理,可以节省大量的计算时间[1]。

最近,内存制造商美光科技和ILT软件提供商D2S合作,在对工艺窗口要求严格的接触层(contact layers)和切割层(cut layers)方面进行了一些测试。数据表明,对工艺窗口有明显的改善作用。

计算光刻技术的作用

遥想当年,整个集成电路制造界,包括英特尔、台积电、三星都在28nm、22nm节点卡壳,想必就是遇到193nm ArF的极限问题。然而现在利用193nm+浸入式技术 +多重图形技术已经完成了7纳米节点工艺,半导体不可谓不神奇。

不过发展到今天,最小可分辨特征尺寸(MRF)已经不同于以往的叫法。xx nm节点不意味着晶体管的结构真有那么小,原先这个数字(xxx nm)是指结构的half pitch,而到了现在“水份”更多,一般是指最小feature-size。所以现在22nm、16nm、14nm、7nm、5nm只是一个技术节点的标志,其对应的最小结构要比节点数字大两倍左右。

这一成绩的取得,也多亏了计算光刻技术,不管OPC、SMO、DPT还是ILT都是对现有光刻工艺技术的一种有效补充,尽可能的增大工艺窗口,提高分辨率。

1、仿真运算加速工艺研发周期。先进工艺必须依赖大量的仿真计算,这样可以在工艺开发初期就对光刻、蚀刻、设计目标协同优化(Design Technology Co-optimization,DTCO)、可制造性设计(Design for Manufacturability,DFM)所协同效应带来的工艺窗口优化、工艺能力分析、材料选择、光源选择、OPC效应,通盘考虑之后,最后通过晶圆实际曝光数据验证,最优化的选取最佳材料、工艺参数、OPC模型。

2、全芯片优化。目前针对图形的OPC,特别是负显影(negative tone develop,NTD)工艺的OPC校准,必须有大量的基于物理与化学模型的OPC算法进行全芯片(full chip)优化,考虑各种3D效应(Mask 3D、Wafer 3D、Resist 3D/R3D),运用大量的物理建模和卷积运算,加上对于光刻胶PEB(Post Exposure Bake)和显影的化学扩散模型,NTD光刻胶的物理弹性形变等等效应的建模计算。

据悉,在进入28纳米工艺节点后,各种不常见的物理现象层出不穷,因此在OPC建模时必须考虑掩模(Mask)、光刻胶(Resist)、晶圆衬底(Wafer Substrate)在3D形貌上的变化对于工艺窗口带来的影响,因此通过R3D(Resist)模型对光源形状(Source Shape)、光瞳形状(Pupil Shape)以及OPC模型进行优化以获得最佳Resist Profiles & CommonOverlapping工艺窗口。

3、光源掩模协同优化成为工艺研发的必须。SMO技术成为先进工艺特别是20纳米以下工艺的必须。因为在先进工艺中,每一个关键层都需要根据设计图形进行光源和光罩图形,包括亚分辨率辅助图形(Sub-Resolution Assist Feature,SRAF)进行最优化调整。如果没有SMO就无法得到最优化的光刻工艺条件,工艺窗口大幅降低,甚至没有。这部分目前由ASML/Brion掌握最核心算法,即使购买ASML的光刻机,也需要单独购买SMO软件。

假如计算光刻软件断供:

1、就会大大增加研发的学习周期(learning cycle),最终事倍功半。

2、根本无法进行电路图形的OPC和对于工艺变化的补偿,最终导致无法实现光刻工艺。

3、在EUV方案中,由于点扩散函数(Point Spread Function,PSF)在OPC建模时非常重要,如果无法获取ASML曝光投影系统的具体beam特性,OPC模型肯定受影响,进而影响到工艺研发。

4、尽管每一代工艺节点都只要一次SMO就可以,但是新产品,由于客户设计千变万化,没有两个设计相同的芯片(否则就侵权了),所以每一个新产品都要进行OPC、DFM、tape out flow,如果没有计算光刻软件支持,新项目将无法进行。

5、即使现有的计算光刻软件,对方也设有时间锁,只要license到期就会锁定,将无法使用。

关键的是,文中提到的计算光刻软件被海外公司垄断,光刻投影系统巨头阿斯麦(ASML)、全球EDA三巨头新思科技(Synopsys)、楷登电子(Cadence)和明导(MENTOR)都有专用的计算光刻软件提供,如阿斯麦ASML的Tachyon/Tflex(由旗下睿初Brion提供)、新思科技的Proteus系列、楷登电子的(Process Proximity Compensation,PPC)、明导的Calibre系列都获得了广泛的应用。

目前国内从事计算光刻技术研究的不多。中国科学院微电子研究所计算光刻研发中心做出了很多有价值的工作,成果被国内主流Fab(包括中芯国际、长江存储)和设计公司采用。还有就是2019年成立的全芯智造主要集中在计算光刻软件的研发。

参考文献:

[1]韦亚一,超大规模集成电路先进光刻理论与应用,科学出版社,2016,338-368

[2]韦亚一,粟雅娟,刘艳松,先导光刻技术中的光学邻近效应修正,微纳电子技术,2014,51(3):186-193

[3]韩明,全芯智造,人工智能赋能半导体制造业-从OPC说开去,芯思想公众号【EDA专栏】;https://mp.weixin.qq.com/s/Sy1mF6X3FL9BnnkWg5eOBw

[4] 李扬环. 反向光刻技术和版图复杂度研究[D]. 浙江大学, 2012. 7-9

鸣谢

本文在成稿过程中,得到杨晓松先生的大力帮助,在此特别感谢!

来源:芯思想,作者:赵元闯